‘20나노 4Gb DDR3 D램’에 적용된 차세대 공정 기술 파헤치기!

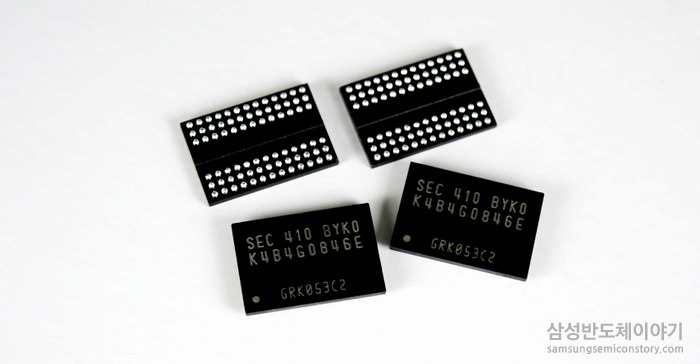

삼성전자가 이 달부터 세계 최초로 차세대 ’20나노(1나노 : 10억분의 1미터) 4기가비트(Giga bit) DDR3(Double Data Rate 3) D램’을 본격 양산하기 시작했습니다. 이번에 양산에 성공한 20나노 D램에 삼성전자의 신개념 ‘개량형 이중 포토 노광 기술’, ‘초미세 유전막 형성 기술’이 동시에 적용됐습니다.

☞ 삼성전자, 세계 최초 ‘20나노 4기가 비트 D램’ 양산

낸드 플래시는 셀(정보저장의 최소단위)이 트랜지스터 하나로 구성되어 구조가 비교적 단순한 반면, D램은 셀이 트랜지스터와 캐패시터 적층구조로 구성되기 때문에 20나노 공정 미세화가 기술적으로 매우 어려웠습니다. 삼성전자는 이러한 D램 미세화 공정의 기술한계를 독자기술인 ‘개량형 이중 포토 노광 기술’과 ‘초미세 유전막 형성 기술’을 통해 극복한 것인데요.

아마 많은 분들이 20나노 D램에 적용된 신개념 ‘개량형 이중 포토 노광 기술’, ‘초미세 유전막 형성 기술’에 대해 궁금증을 가지셨을 겁니다. 이름만 들어도 어렵게 느껴지는 이 기술들은 과연 어떤 점에서 기존 기술과 차이가 있는 걸까요? 그리고 새로운 기술들을 적용했을 때는 어떤 장점이 있는 걸까요? 오늘은 삼성반도체이야기가 쉽고 간략하게 소개해 드리겠습니다!

■ ‘개량형 이중 포토 노광기술’, ‘초미세 유전막 형성기술’ 독자 기술로 공정 한계 극복

개량형 이중 포토 노광 기술

노광 기술(포토 리소그래피, Photo lithography)은 반도체 공정에서 웨이퍼 위에 감광액을 바르고 빛을 통과시킨 뒤 미세 회로를 그리는 기술입니다. 여기에 이중 포토(더블 패터닝, Double Patterning) 기술은 미세한 회로를 만들기 위해 회로를 두 번에 나눠 그리는 것인데요. 즉, 하나의 회로 패턴을 완성하기 위해 같은 자리에 노광 공정을 두 번씩 진행하는 것을 말합니다.

이렇게 두 번 노광을 진행할 경우 미세한 차이가 생길 수 있습니다. 노광 공정은 나노미터 단위의 섬세한 공정이기 때문에 빛 파장의 베리에이션으로 1나노미터의 오차가 발생하면 20나노미터의 회로가 양옆으로 1나노미터씩 늘어나 22나노미터 회로가 되고, 2나노미터의 오차가 발생하면 24나노미터 회로가 되는 것입니다.

특히 동작 속도가 빠른 4Gb D램의 경우 40억 개가 넘는 셀들에 특성 불량이 발생하지 않도록 조금의 오차도 없이 정확하게 그려야 하므로 더욱 어려운 과정이라고 할 수 있습니다.

하지만 삼성전자는 이번에 개량형 이중 포토 노광 기술을 개발함으로써 고속 동작에도 안정적으로 동작하도록 정확히 20나노미터에 맞춰 회로를 구성할 수 있게 되었습니다. 이로써 20나노 D램의 생산 비중을 빠르게 늘리고, 차세대 10나노급 D램도 적기에 양산할 수 있는 기반기술을 마련하게 되었습니다.

초미세 유전막 형성기술

D램은 셀을 구성하는 캐패시터에 전하가 있는지(1) 없는지(0)의 여부에 따라 0과 1의 디지털 신호를 구분합니다. D램 셀은 특성상 캐패시터 내의 전하 값을 매우 짧은 기간만 저장할 수 있는데요. 이 때문에 컴퓨터에서는 CPU의 주기에 맞춰 64ms로 리프레시 동작 모드를 통해 주기적으로 셀에 전기를 공급합니다. 하지만 셀 불량으로 전자가 리프레시 되기도 전에 방전되는 경우 전하 값이 달라지면서 원래 값을 인식하지 못하고 반도체가 오작동을 하게 되는데요.

따라서 캐패시터를 만들 때에는 전하가 너무 빠르게 새거나 옆 캐패시터 전하의 영향을 받아서 전하가 빠져 나가지 않도록 유전막을 형성합니다. 이 유전막은 전기선의 플라스틱 피복선 같은 절연막 역할을 하는데, 여기서 유전막의 균일성을 유지하는 것이 반도체 제조의 핵심공정이라고 할 수 있습니다.

삼성전자는 초미세 유전막 형성 기술을 통해 셀 캐패시터의 유전막 형성 물질을 옹스트롬(10분의 1나노) 단위로 초미세 제어함으로써 20나노에서도 우수한 셀 특성을 확보했습니다. 기존에 분자 단위의 물질을 사용하던 나노 공정을 나노의 1/10인 옹스트롬 단위의 원자구조 물질을 사용해 균일한 유전막을 만든 것입니다.

기존에 분자 물질로 유전막을 만들 경우에는 입자가 커서 균일한 막질을 형성하기 어려운데다 분자보다 엄청나게 작은 전자가 새지 않도록 유전막층을 더욱 두껍게 발라야 하는 어려움이 있었습니다. 그럴 경우 유전막층이 두꺼워져 트랜지스터 내의 전하의 저장량은 대폭 줄어들게 되는데요. 같은 조건에서 20나노 캐패시터를 만들 경우, 분자구조로는 더 작아진 트랜지스터에 균일한 유전막을 만들기가 매우 어려울 뿐만 아니라 전하의 저장량도 현격히 줄어들게 된다는 점입니다.

그래서 바로 25나노 캐패시터보다도 훨씬 작은 20나노 캐패시터에서 유전막이 얼마나 얇고 촘촘하게 작게 만들 수 있는지가 20나노 공정의 성공의 관건이 되었습니다. 이번에 양산에 성공한 20나노 D램은 물질의 최소단위인 원자 물질을 사용해 유전막을 형성함으로써 얇은 막으로도 촘촘한 절연층을 형성했기 때문에 셀을 구성하는 캐패시터에서 전하가 새지 않는 우수한 특성을 확보할 수 있었습니다.

기술 한계를 극복한 삼성전자의 20나노 4기가비트 DDR3 D램! 이 작은 칩안에 적용된 삼성전자의 신개념 기술들에 대해 조금은 이해가 되셨나요? 이를 통해 20나노 DDR3 D램 모듈은 PC에서 기존 25나노 대비 소비전력을 25% 절감할 수 있을 뿐만 아니라 글로벌 IT 업체들에 최고 수준의 ‘초절전 그린 IT 솔루션’을 제공하게 되었습니다. 초고속, 저전력, 고용량을 위한 삼성전자의 기술 혁신은 계속 됩니다! 앞으로도 삼성반도체이야기가 더 쉽고, 더 빠르게 반도체의 최신 기술 소식들을 여러분께 소개해 드릴게요~

▶ 출처 : 삼성 투모로우 (http://samsungtomorrow.com/)