삼성전자, AI•차세대 슈퍼컴퓨터용 초고속 D램 세계최초 출시

삼성전자가 차세대 슈퍼컴퓨터(HPC)와 인공지능(AI) 기반 초고속 데이터 분석에 활용될 수 있는 초고속 D램, ‘플래시볼트(Flashbolt)’를 출시했습니다.

10나노급(1y) 16기가비트(Gb) D램 8개 쌓아 최고용량(16GB) 구현

‘플래시볼트’는 16기가바이트(GB) 용량의 3세대 HBM2E(고대역폭 메모리, High Bandwidth Memory 2 Extended) D램으로 기존 2세대 대비 속도와 용량이 각각 1.3배, 2.0배 향상됐습니다.

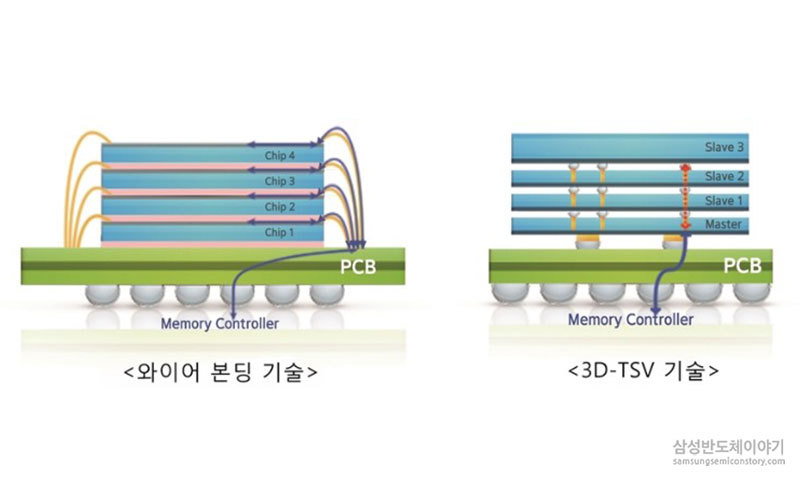

| ※ HBM : 고대역폭 메모리로, TSV 기술을 적용해 기존의 금선을 이용한 일반 D램 패키지에 비해 데이터 처리 속도를 혁신적으로 끌어올린 제품 |

삼성전자는 2세대 8GB HBM2 D램 ‘아쿠아볼트(Aquabolt)’를 세계 최초로 개발해 업계에서 유일하게 양산한 지 2년만에 3세대 HBM2E D램 ‘플래시볼트’를 출시하며 차세대 프리미엄 메모리 시장 선점에 나섰습니다.

‘플래시볼트’는 1개의 버퍼 칩 위에 16기가비트(Gb) D램 칩(10나노급) 8개를 쌓아 16GB 용량을 구현해 차세대 고객 시스템에서 최고용량, 최고속도, 초절전 등 최적의 솔루션을 제공합니다.

| ※ 8Gb = 1GB, 16Gb = 2GB ※ 3세대 HBM2E: 16GB (16Gb D램 x 8개) / 2세대 HBM2: 8GB (8Gb D램 x 8개) |

삼성전자는 16Gb D램 칩에 5,600개 이상의 미세한 구멍을 뚫고 총 4만개 이상의 TSV 접합볼로 8개 칩을 수직 연결한 ‘초고집적 TSV 설계 기술’을 이 제품에 적용했습니다.

특히 이 제품은 ‘신호전송 최적화 회로 설계’를 활용해 총 1,024개의 데이터 전달 통로에서 초당 3.2기가비트의 속도로 410기가바이트의 데이터를 처리합니다. 풀HD(5기가바이트) 영화 82편을 1초에 전달할 수 있는 수준입니다.

| ※ 2세대 HBM2 = 초당 2.4Gb 속도로 307GB 전송 가능, 영화 61편 수준 |

향후 차세대 HBM D램 선행 개발로 프리미엄 메모리시장 성장 견인

삼성전자는 2020년 이 제품을 양산해 기존 인공지능 기반 초고속 데이터 분석과 고성능 그래픽 시스템을 개선하고 슈퍼컴퓨터의 성능 한계를 극복해 차세대 고성능 시스템 적기 개발에 기여할 계획입니다.

이 제품은 또 세계 최초로 초당 4.2기가비트까지 데이터 전달 속도 특성을 확보해 향후 특정 분야의 차세대 시스템에서는 538기가바이트를 1초에 처리할 수 있을 것으로 전망됩니다.

2세대 제품과 비교할 경우 초당 데이터 처리 속도가 1.75배 이상 향상되는 것입니다.

삼성전자 메모리사업부 전략마케팅실 최철 부사장은 “역대 최고 성능의 차세대 D램 패키지 출시로 빠르게 성장하는 프리미엄 시장에서 사업 경쟁력을 계속 유지할 수 있게 되었다”며, “향후 더욱 차별화된 솔루션을 제공해 독보적인 사업 역량을 강화시켜 나갈 것”이라고 강조했습니다.

삼성전자는 글로벌 IT 고객들에게 ‘아쿠아볼트’를 안정적으로 공급하는 한편, 차세대 시스템 개발 협력을 더욱 강화해 ‘플래시볼트’ 시장을 확대함으로써 프리미엄 메모리 시장의 수요 확대를 적극 주도해 나갈 계획입니다.

[참고]

□ HBM (High Bandwidth Memory)

최신 인공지능 서비스용 슈퍼컴퓨터, 네트워크, 그래픽카드 등의 프리미엄 시장에 최적의 솔루션을 제공하는 고대역폭 메모리

□ TSV(Through Silicon Via, 실리콘 관통 전극)

D램 칩을 일반 종이(100μm)두께의 절반수준으로 깎은 후, 수천 개의 미세한 구멍을 뚫고, 상단 칩과 하단 칩의 구멍을 수직으로 관통하는 전극으로 연결한 최첨단 패키징 기술

□ 삼성전자 TSV기술 기반 D램 제품 개발/양산 연혁

• 2010.12월: 40나노급 8GB 3D TSV DDR3 RDIMM 개발

• 2011.08월: 30나노급 32GB 3D TSV DDR3 RDIMM 개발

• 2014.08월: 20나노급 64GB 3D TSV DDR4 RDIMM 양산

※ CES 2015 ECO Tech부문 '혁신상' 수상

※ 2015년 제25주차 IR52 장영실상 '장관상' 수상 • 2015.10월: 20나노 128GB 3D TSV DDR4 RDIMM 양산

• 2015.10월: 20나노 4GB HBM2 D램 개발

• 2015.12월: 20나노 128GB 3D TSV DDR4 LRDIMM 양산

• 2015.12월: 20나노 4GB HBM2 D램 양산

※ 2016년 멀티미디어 기술대상 '장관상' 수상• 2016.06월: 20나노 2.0Gbps 8GB HBM2 D램(Flarebolt) 양산

• 2017.12월: 20나노 2.4Gbps 8GB HBM2 D램(Aquabolt) 양산

• 2020.01월: 10나노급 3.2Gbps 16GB HBM2E D램(Flashbolt) 양산