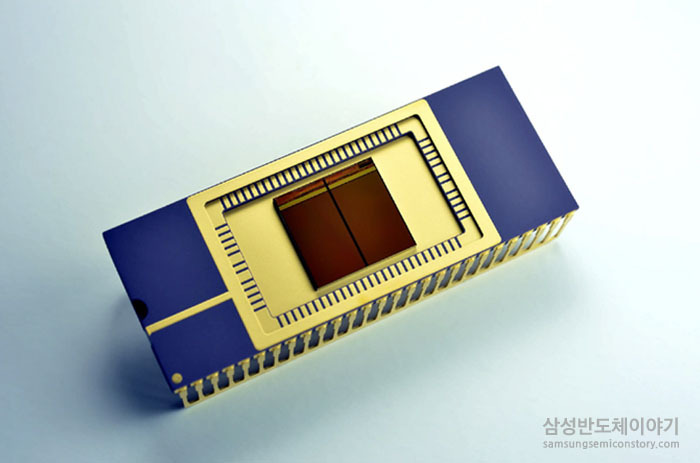

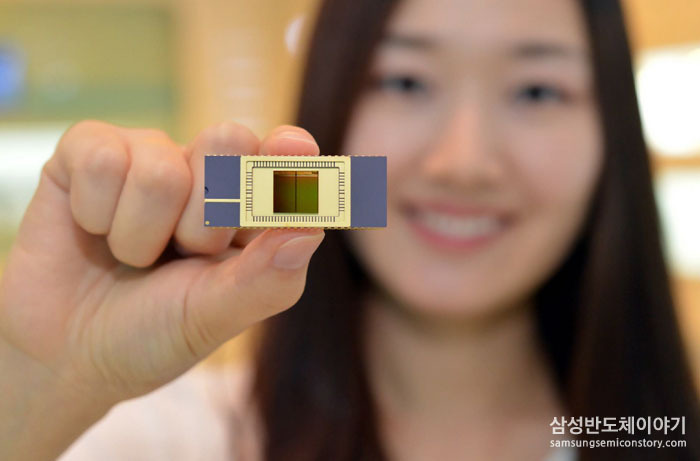

삼성전자, 세계 최초 3차원 수직구조 낸드(3D V-NAND)플래시 메모리 양산

삼성전자가 세계 최초로 3차원 메모리 반도체 시대를 열었습니다.

삼성전자는 6일 반도체 미세화 기술의 한계를 극복한 신개념 3차원 수직구조 낸드(3D Vertical NAND, 3D V-NAND) 플래시 메모리의 양산을 시작했다고 밝혔는데요.

이번 3차원 수직구조 낸드플래시 메모리는 업계 최대 용량인 128기가비트(Gigabit) 제품입니다.

■ 삼성 독자 기술로 반도체 기술 한계 극복

삼성전자의 독자 기술 ‘3차원 원통형 CTF(3D Charge Trap Flash) 셀구조’와 ‘3차원 수직적층 공정’ 기술이 동시 적용된 이 제품은 기존 20나노급 대비 집적도가 2배 이상 높아 생산성이 대폭 향상됐습니다.

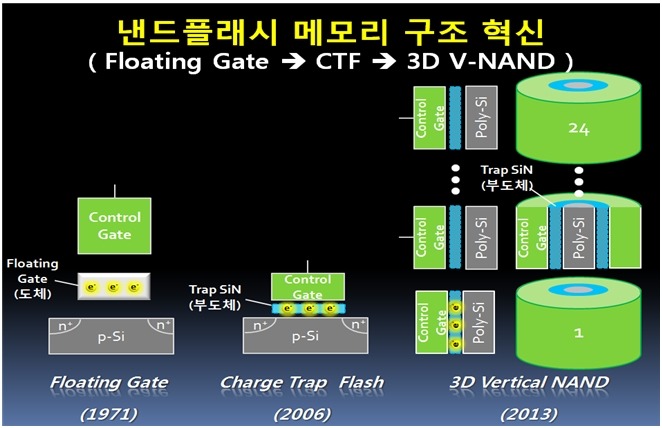

지금까지 양산된 낸드플래시 메모리는 게이트에 전하를 저장하는 방식으로 40여 년 전 개발된 플로팅 게이트(Floating Gate) 구조를 적용했습니다.

그러나 최근 10나노급 공정 도입으로 셀간 간격이 대폭 좁아져 전자가 누설되는 간섭 현상이 심화되는 등 미세화 기술은 물리적 한계에 도달했는데요.

이에 삼성전자는 단층으로 배열된 셀을 3차원 수직으로 적층하는 ‘구조 혁신’과 ‘공정 혁신’을 통해 모든 문제점을 한 번에 극복하고 업계 최초로 ‘3차원 메모리 양산시대’를 열었습니다.

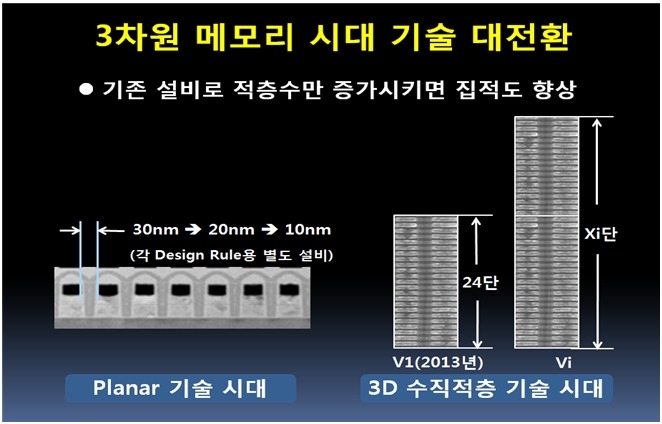

■ 미세화 경쟁에서 수직적층 경쟁으로 메모리 기술 대전환

삼성전자가 수 년간의 연구를 통해 개발한 ‘3차원 원통형 CTF셀 구조’ 기술은 고층빌딩처럼 수직 24단을 쌓는 것으로 삼성전자가 세계 최초로 개발한 2차원 CTF 기술을 입체 기술로 발전시킨 것입니다.

‘3차원 원통형 CTF 셀’은 전하를 안정적인 부도체에 저장해 위 아래 셀간 간섭 영향을 대폭 줄여 줍니다.

이로 인해 쓰기속도는 2배 이상 빨라지고 셀 수명인 쓰기 횟수(내구 연한)는 제품별로 최소 2배에서 최대 10배 이상으로 대폭 향상되며 소비전력 또한 절반으로 감소되었습니다.

‘3차원 수직적층 공정’은 더 작은 칩 면적에서 최고 집적도를 실현하는 기술로 삼성전자는 높은 단에서 낮은 단으로 구멍을 뚫어 전극을 연결하는 에칭(Etching) 기술과 각 단 홀에 수직 셀을 만드는 게이트 패턴 기술 등 독창적이고 획기적인 공정 기술을 개발했습니다.

또한 삼성전자는 지난 10년간 ‘3차원 수직구조 낸드플래시’를 연구하면서 300여건 이상의 핵심 특허를 개발해 한국, 미국, 일본을 비롯한 세계 각국에 출원을 완료했습니다.

삼성전자는 10나노급 이하 반도체 기술의 한계를 뛰어 넘어 향후 1테라(Tera) 비트 이상 낸드플래시를 출시할 수 있는 원천 기술을 확보하면서 낸드플래시 기술을 이끌어 나갈 패러다임을 제시했습니다.

결국 향후 낸드시장은 최신 포토설비를 이용한 미세화 경쟁 대신 적층 수를 높이며 고용량을 실현하는 기술 대전환을 이루게 됐습니다.

삼성전자 메모리사업부 플래시개발실장 최정혁 전무는 “수 년간 임직원 모두가 기술적 한계 극복을 위해 혁신 기술 개발에 매진한 결실”이라며 “향후 지속적으로 집적도를 높이고 성능을 향상시킨 차세대 제품을 연이어 출시해 세계 IT 산업 발전에 기여할 것”이라고 말했습니다.

시장 조사기관에 의하면 세계 낸드플래시 메모리 시장은 올해 236억불에서 2016년 308억불로 지속 성장할 것으로 보입니다.

삼성전자는 세계 최초로 3차원 수직구조 낸드플래시를 양산해 절대적인 제품 경쟁력 우위를 확보한 데 이어, 향후 더욱 차별화된 독자 기술로 메모리 사업 경쟁력을 지속 강화해 나갈 예정입니다.

| ※ 낸드플래시 메모리(NAND Flash Memory) 전원이 꺼져도 데이터가 그대로 저장되는 메모리 반도체로, 스마트폰 등에 음악, 사진, 동영상 등을 저장하는 역할을 한다. 또한 HDD를 대체하는 SSD(Solid State Drive)에도 탑재된다. ※ 플로팅 게이트 구조(Floating Gate) 낸드플래시에서 데이터를 저장하는 기본 단위인 셀 구조로 기존 낸드플래시는 컨트롤 게이트와 플로팅 게이트로 구성되어 도체인 플로팅 게이트에 전하를 저장한다. 10나노 이하 미세화를 진행하게 되면 셀간 간섭이 심해져 공정 미세화가 어렵다. ※ CTF 구조(Charge Trap Flash) 컨트롤 게이트 하나로 구성되어 있고, 기존 플로팅 게이트 대신에 치즈같은 모양의 부도체 빈공간에 전하를 저장하는 방식이다. 게이트가 한 개여서 높이가 낮고, 부도체를 사용하여 셀간 간섭이 작아 상대적으로 미세화가 더 용이하다. ※ 3차원 CTF 구조(3D Charge Trap Flash) 기존 단층 구조의 CTF를 3차원 구조로 개량하여 컨트롤 게이트를 기존 직사각형이 아닌 반지와 같은 원통형으로 만들어 공간 사용을 극대화하고, 적층 공정을 용이하게 해준다. |

※ 낸드 플래시 구조 비교 그림