[반도체 8대 공정] 5탄, 반도체 회로패턴의 완성 ‘식각 공정’

지난 시간에는 준비된 웨이퍼 위에 반도체 회로를 그려 넣는 포토공정(Photo)에 대해 소개해드렸는데요. 포토공정이 끝나면 필요한 회로 패턴을 제외한 나머지 부분을 제거하는 공정이 필요합니다. 이번 시간에는 반도체의 구조를 형성하는 패턴을 만드는 식각공정(Etching)에 대해 알아보겠습니다.

동판화 에칭(Etching) 기법과 비슷한 식각공정

학창 시절, 미술시간에 한 번쯤 만들어봤던 ‘판화’는 회화의 한 장르인데요. 나무·금속·돌 등의 면에 형상을 그려 판을 만든 다음, 잉크나 물감을 칠하여 종이나 천에 인쇄하는 방식이죠. 식각공정은 이러한 판화 기법의 한 종류인 에칭(Etching)과 비슷한 원리를 가지고 있습니다.

회화에서 에칭 기법은 산의 화학작용을 방지하는 방식제(그라운드)를 바른 동판을 날카로운 도구를 이용하여 긁어내 동판을 노출시키는 과정을 말합니다. 이때 동판을 부식액(묽은 질산)에 넣고, 부식의 진행 정도를 조절하여 이미지를 만드는 것인데요.

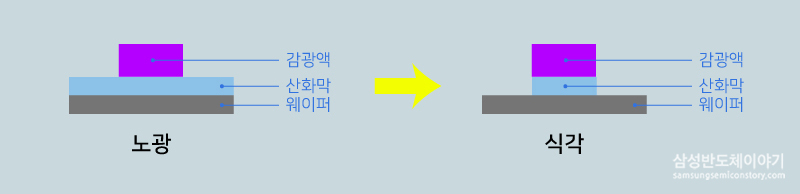

부식과 같은 화학작용을 이용해 이미지를 만드는 판화의 에칭 기법처럼, 반도체 식각공정도 웨이퍼에 액체 또는 기체의 부식액(etchant)을 이용해 불필요한 부분을 선택적으로 제거한 후 반도체 회로 패턴을 만듭니다.

포토공정에서 형성된 감광액 부분을 남겨둔 채 나머지 부분을 부식액을 이용해 벗겨 냄으로써 회로를 형성하죠. 식각이 끝나면 감광액도 제거합니다. 이렇게 반도체를 구성하는 여러 층의 얇은 막에 원하는 회로 패턴을 형성하는 과정을 반복하는데요.

식각공정은 식각 반응을 일으키는 물질의 상태에 따라 습식(wet)과 건식(dry)으로 나뉩니다. 건식 식각(Dry Etching)은 반응성 기체, 이온 등을 이용해 특정 부위를 제거하는 방법이며, 습식 식각(Wet Etching)은 용액을 이용 화학적인 반응을 통해 식각하는 방법입니다.

건식은 습식에 비해 비용이 비싸고 방법이 까다로운 단점이 있으나, 최근에는 나노 단위로 고집적화되는 반도체 기술 변화에 따라 회로선폭 역시 미세해지고 있습니다. 이에 따라 수율을 높이기 위한 방법으로 습식(Wet)보다는 건식(Dry) 식각이 확대되고 있죠.

불필요한 부분을 선택적으로 없애는 건식 식각

그렇다면, 건식 식각(Dry etching)은 어떠한 방법을 통해 회로 패턴 이외에 불필요한 부분을 제거하는 것일까요?

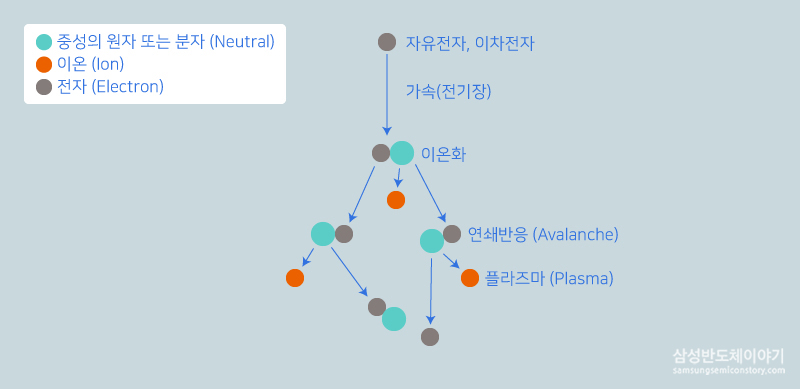

건식 식각은 플라즈마(Plasma) 식각이라고도 합니다. 일반 대기압보다 낮은 압력인 진공 챔버(Chamber)에 가스를 주입한 후, 전기 에너지를 공급하여 플라즈마를 발생시키는데요. 플라즈마는 고체-액체-기체를 넘어선 물질의 제 4 상태로 많은 수의 자유전자, 이온, 중성의 원자 또는 분자로 구성되어 이온화된 기체를 말합니다. 이온화는 전기적으로 중성인 원자 또는 분자가 자신이 보유하고 있던 전자를 떼어 내거나 추가 확보함으로써, 양전하 또는 음전하 상태로 바뀌는 현상을 뜻하죠.

또한 플라즈마는 전기에너지에 의해 형성된 충분한 크기의 자기장이 기체에 가해질 때, 기체가 충돌하고 이온화됨으로써 발생하는데요. 즉, 자기장이 자유전자를 가속화시켜 높은 에너지를 가진 자유전자가 중성의 원자나 분자와 충돌하여 이온화를 일으키게 되는 것입니다.

이때 이온화에 의해 생성된 추가 전자도 연쇄 반응(Avalanche)에 의해 또 다른 이온화를 일으키면서 이온의 수가 기하급수적으로 늘어나게 됩니다. 이 상태를 바로 ‘플라즈마 상태’라고 하는데요. 플라즈마 상태에서 해리된 반응성 원자(Radical Atom)가 웨이퍼 위를 덮고 있는 막질 원자와 만나 강한 휘발성을 띠면서 표면에서 떨어져 나가게 됩니다. 이러한 반응을 통해 감광액(PR, Photo Resist) 보호막으로 가려져 있지 않은 막질은 제거되는 것이죠.

건식 식각 과정에서는 몇 가지 유의해야 할 사항들이 있습니다.

첫 번째는 균일도(Uniformity)를 유지하는 것인데요. 균일도란 식각이 이루어지는 속도가 웨이퍼 상의 여러 지점에서 ‘얼마나 동일한 가’를 의미합니다. 일정한 시간 동안 공정을 진행한 상태에서 웨이퍼의 부위에 따라 식각 속도가 다를 경우, 형성된 모양이 부위별로 다르게 되어 특정 부위에 위치한 칩에 불량이 발생하거나 특성이 달라지는 문제가 발생할 수 있기 때문입니다.

두 번째는 식각 속도(Etch Rate)입니다. 이는 일정 시간 동안 막질을 얼마나 제거할 수 있는지를 의미하는데요. 식각 속도는 주로 표면 반응에 필요한 반응성 원자와 이온의 양, 이온이 가진 에너지에 의해서 변화합니다. 즉 이러한 인자의 조절 능력을 높여 전체적인 수율을 향상시키기 위해 노력하고 있는데요. 이 밖에도 선택비(Selectivity), 형상(Profile) 등이 건식 식각의 주요 인자로 중요하게 여겨지고 있습니다.

지금까지 반도체 회로 패턴을 완성하는 식각 공정(Etching)에 대해 알아봤습니다. 집적회로 기술의 산물인 반도체는 필요 물질의 박막(Thin Film)을 실리콘 기판 전면에 바른 후 남기고자 하는 모양에 보호층을 덮어 이외의 부분을 깎아내는 작업을 여러 번 반복해 제작되는데요. 이 모든 공정은 안전하게 설계된 장비 안에서 이루어지죠.

다음 시간에는 식각공정에 이어 반도체가 원하는 전기적 특성을 갖출 수 있도록 웨이퍼 위에 씌우는 얇은 막을 뜻하는 ‘박막(thin film)’공정에 대해 알아보도록 하겠습니다.